# **1. Introduction**

### **1.1 Introduction to GMRT:**

The Giant Metrewave Radio Telescope (GMRT), located near Pune in India, is the world's largest array of radio telescopes at meter wavelengths. It is operated by the National Centre for Radio Astrophysics, a part of the Tata Institute of Fundamental Research, Mumbai.

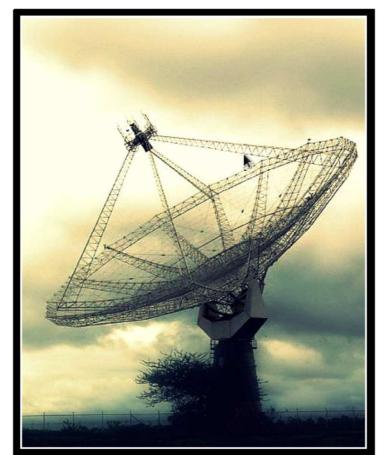

The GMRT contains 30 fully steerable telescopes, each 45 meters in diameter spread over distances of upto 25 km. The design of these antennas is based on the **`SMART'** concept - Stretch Mesh Attached to Rope Trusses. The reflector made of wire rope stretched between metal struts in a parabolic configuration. This configuration works fine as the telescope operates at long wavelengths (21 cm and above). Every antenna has four different receivers mounted at the focus. Figure 1.1 shows one such antenna. Each individual receiver assembly can rotate, enabling the user to select any of them for the observation. GMRT antennas operate in five frequency bands, centered at 153, 233, 327, 610, and 1420 MHz. All these feeds provide dual polarization outputs. In some configurations, dual-frequency observations are also possible.

Figure. 1.1 Antenna

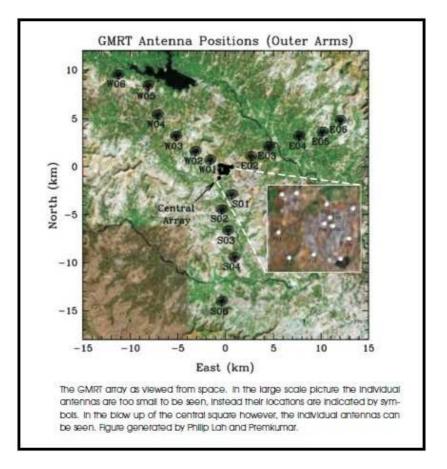

Out of the 30 telescopes at GMRT, fourteen telescopes are randomly arranged in the central square of 1 km by 1 km in size. Rest sixteen telescopes are arranged in three arms of a nearly —'Y'-shaped array each having a length of 14 km from the array centre. The positions of the antennas in the antenna array have been shown in Figure 1.2.

Figure. 1.2 Antenna Array at GMRT

Therefore GMRT can act as an interferometer which uses a technique known as aperture synthesis to make images of radio sources. The multiplication or correlation of radio signals from all the 435 possible pairs of antennas or interferometers over several hours will thus enable radio images of celestial objects to be synthesized with a resolution equivalent to that obtainable with a single gigantic dish 25 kilometer in diameter! The maximum baseline in the array gives the telescope an angular resolution (the smallest angular scale that can be distinguished) of about 1 arc-second, at the frequency of neutral hydrogen. To provide seamless coverage from 100 MHz to 1600 MHz in addition to upgrades to the mechanical and servo control systems to the antenna and an improved high speed telemetry system for controlling the antennas remotely. This needs a major upgrade to the backend electronics, two possible solutions to the backend upgrade are currently being developed – one based on multiple FPGA boards, and second on GPU cluster.

Currently, the GMRT is undergoing an upgrade. As part of the upgrade, the GMRT plans to increase the bandwidth of the GMRT from the present value of 32 MHz to about 400 MHz and also plans to upgrade the digital backend from GSB (GMRT software Backend) to FPGA and GPU based backend.

#### **1.2. Introduction to digital backend:**

The digital backend is responsible for digital signal processing of the telescopic data used in interferometer and beamforming modes.

The digital signal is processed through FX Correlator (FX : FFT followed by Multiplier) to generate cross amplitude and phase information between each pair (baseline) among the 30 antennas to give the visibility information.

This data is used in imaging, continuum and many other astronomical observations.

#### **1.3. Introduction to the project:**

The Project of implementing and testing incoherent Packetized Beamformer is a part of the upgradation process of GMRT Backend system.

In Radio astronomy, beamforming is a technique which is used to get the pulsar profile. It can be of two types such as, Incoherent beamforming mode and coherent beamforming mode. The incoherent beamformer adds voltage signals from different antennae and computes the basic self term of voltage signals of the two polarizations. This incoherent beamformer for 4 antennae and 2 orthogonal polarizations is implemented on a multiple ROACH-boards (FPGA platform) and tested with proper pulsar source.

#### **1.4. Significance of the project:**

Pulsars are weak radio sources, and their individual pulses often do not rise above the background noise, so even with long base line it appears as a point source. Beamforming is the standard signal processing technique for its study to get its profile in higher resolution. Incoherent beamformer exhibits a higher sensitivity by  $\sqrt{N}$  times (N= no of antennae). As the voltage signals of different antennae are squared and added, the incoherent beamformer provides vital information of the pulsars. So as a part upgradation process of GMRT backend, incoherent beamformer is implemented on FPGA.

FPGA is chosen as a hardware platform for its re-configurable features and better computing resources with lesser power conservation and higher bandwidth compared to the software based solution.

Within the scope of our project, we need to design the basic hardware and its interfacing utilities and test it with real time sources. So, the 4 antennae and 2 polarizations incoherent beamformer is implemented on multiple Virtex-5 pro FPGA (ROACH-board) to verify the functioning of the incoherent beamforming.

### **1.5.** Aim and Objectives of the project:

The aim of this project is to design and implement incoherent packetized beamformer on multiple ROACH boards (FPGA platform) for 4 antennae 2 polarizations and test the design with Pulsars to get the pulsar profile.

The objectives of the project are:

- Design and implement the incoherent beamformer for 4 antennae and 2 polarizations on multiple FPGA platform (ROACH-board).

- Write scripts for the necessary interfacings of the ROACH-board with host PC.

- Simulation and implementation of design on hardware for verifying design logic.

- Verify the design using sky-test, i.e. testing with signals from radio sources (Pulsar).

## 1.6. Casper:

The <u>Center for Astronomy Signal Processing and Electronics Research (CASPER) is a global</u> collaboration dedicated to streamlining and simplifying the design flow of radio astronomy instrumentation by promoting design reuse through the development of platform-independent, open-source hardware and software.

The CASPER tool flow is better known as the MSSGE (Matlab/Simulink/System Generator/EDK) or bee xps tool flow. It is the platform for FPGA-based CASPER development and is the interface between several design and implementation environments.

Casper design environment in GMRT that is used during the course of this project use following version of different utility

- Matlab R2008a (v7.6.0)

- Simulink R2008b (v7.2)

- Xilinx System Generator v10.1.3.1386

- Xilinx EDK v11.5

- Xilinx ISE v11.5

- MSSGE libraries

The aim is to couple the real-time streaming performance of application-specific hardware with the design simplicity of general-purpose software. By providing parameterized, platform independent "gateware" libraries that run on reconfigurable, modular hardware building blocks, CASPER abstracts away low-level implementation details and allow astronomers to rapidly design and deploy new instruments.

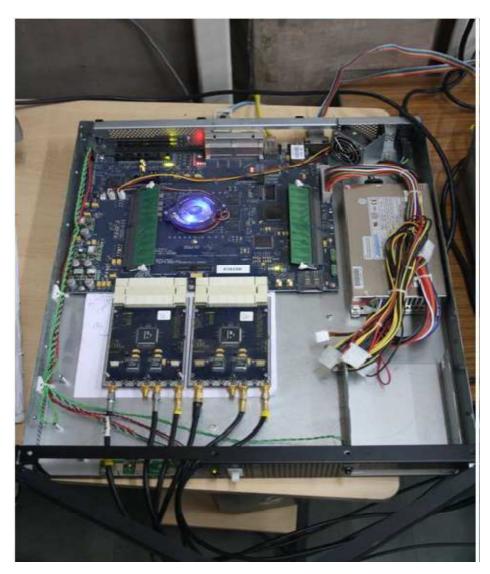

CASPER instruments use reconfigurable open-source hardware built around Xilinx FPGAs. The GMRT uses Virtex 5 SXT95 based standalone FPGA processing board also called ROACH (Reconfigurable Open Architecture Computing Hardware). Figure 1.3 is an image of one such ROACH board. The ROACH board also has the Following features:

• A separate PowerPC runs Linux and is used to control the board

CX4/XAUI/10GbE Networks Interfacing Cards

• ADC2x1000-8: Dual 8-bit, 1000Msps (or single 8-bit 2000Msps), Atmel/e2v AT84AD001B ADC

Figure. 1.3 Virtex 5 ROACH board

# **2. Theoretical concepts**

## 2.1. Interferometry and correlator:

Interferometry is a technique in which waves are superimposed in such a way that one can analyze wave property from residual phase and spectrum. Interferometry makes use of the principle of superposition to combine waves in a way that will cause the result of their combination to have some meaningful pattern that is diagnostic of the original state of the waves. This works because when two waves with the same frequency combine, the resulting pattern is determined by the phase difference between the two waves— waves that are in phase will undergo constructive interference while waves that are out of phase will undergo destructive interference.

A radio interferometer measures the mutual coherence function of the electric field due to a given source brightness distribution in the sky. The antennas of the interferometer convert the electric field into voltages. The mutual coherence function is measured by cross correlating the voltages from each pair of antennas. The measured cross correlation function is also called Visibility. In general it is required to measure the visibility for different frequencies (spectral visibility) to get spectral information for the astronomical source.

The cross correlation between two signals *s*<sub>1</sub>*t* and *s*<sub>2</sub>*t*

$$R_c \tau = < s_1 t s_2 t + \tau >$$

Where  $\tau$  the time delay between the two signals and angle brackets is indicates averaging in time.

According to Wiener-Khinchin theorem which says, the power spectral density (PSD) of a stationary stochastic process is defined to be the FT of its auto-correlation function that is if

$$R_c \tau = < s_1(t)s_2(t+\tau) >$$

then power spectral density function  $S_c f$  is

$$S_c(f) = \int_{-\infty}^{\infty} R_c(\tau) e^{-j2\pi f\tau} d\tau$$

From the property of Fourier transform we have

$$R_{c}(0) = \langle s_{1}(t)s_{2}(t) \rangle = \int_{-\infty}^{\infty} S_{c}(f) df$$

## **2.2. Beamforming- coherent and incoherent:**

Pulsars are the weak radio sources, so their individual pulses often do not rise above the background noise level. Beamforming is the basic technique used for their studies. Beamforming is a signal processing technique used in sensor arrays for directional signal transmission or reception. This is achieved by combining elements in the array in such a way that signals at particular angles experience constructive interference while others experience destructive interference. In beamformer, the antennae signals can be added coherently or incoherently.

#### **Incoherent Beamforming:**

• In incoherent beamformer, the voltage signals are firstly converted into power spectra. Then the power signals from the N dishes are combined to give the single incoherent beam. As the power spectra of the signals are added, the phase information is lost and no need of phase corrections.

- Root of N improvement in sensitivity.

- Beamwidth of single antenna.

- Application in large scale pulsar search

- The mathematical representation of the incohernt beamformer:

$$B_i = (V_1^2 + V_2^2)$$

This approach is used in the all the design in the course of this work.

#### **Coherent beamformer:**

• Voltage signals from the N dishes are combined to give the single coherent beam. As the voltages are added, it should be in phase with each other to get the resultant coherent signal referred as beam.

- N times improvement in sensitivity

- Beamwidth becomes narrower than the single antenna by nearly 1/N times.

- Application in studies individual known pulsars with its polarimetry studies.

- The mathematical representation of the coherent beamformer

$B_i = (V_1 + V_2)^2$

## 2.3. Pulsar observations requirements:

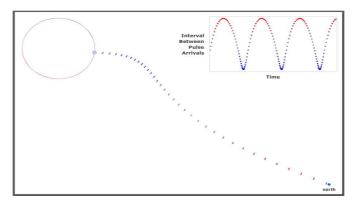

A pulsar is a rapidly rotating neutron star, highly magnetized which emits electromagnetic radiation beams from its magnetic poles as it rotates. The radiation is visible to us only if one of the poles points toward the earth. This appears to us as a very regular series of pulses with a period beam as low as milliseconds. The compact nature of its emission makes it a point source even for largest baseline on the earth.

Figure 2.1: Radiation from pulsar

# **3. Packetized Beamformer Specifications**

- Number of antennas: 4

- Polarization: Both polarization

- Number of spectral channels: 512

- Number of F engines: 4

- Number of X-engines: 8

- Number of spectral channels per X-engine:64

- Networks used: 1Gbps, XAUI link and 10 Gb Ethernet.

- Clock Frequency: 800 MHz

- Bandwidth : 400 MHz

- Base integration time: 0.163 milliseconds

- Data rate from 1 X-engine: 27.19 Mbps.

- Data rate from 8 X-engines: 223.2 Mbps.

# **4. Description of the project work:**

## 4.1. Four Antenna Packetized Beamformer Design:

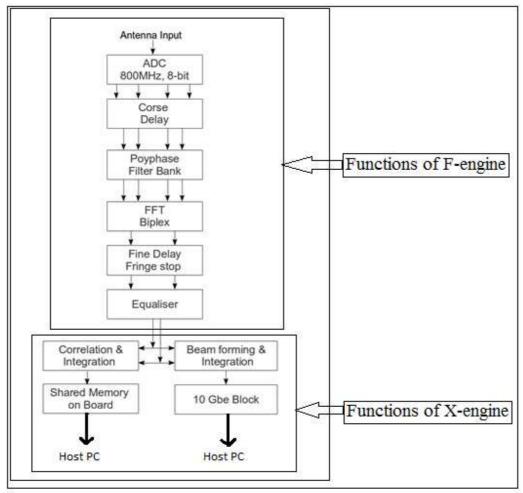

4 antenna packetized beamformer uses four F-engines and 8 X-engines.

Figure 3.1 shows the function performed by an F-engine and also shows after which stage the signal for beamforming is taped.

Figure 4.1. Functions performed by an F-engine

Each block mentioned Figure (3.1) is explained in brief below:

1. <u>ADC:</u> The ADCs interfaced to the ROACH board are ADC2x1000-8. They normally operate at 800MHzand give an 8 bit output through 4 channels each operating at 200MHz. This is done as the FPGA operates at 200MHz. In our design, the ADC is running at 400MHz clock frequency.

2. <u>Delay</u>: The radio sources in the sky are in motion over the sky. This differential change in position of the radio sources with respect to the antennas gives some delays. Other than that, the propagation delays from the antennas to the receiver are also considered. The whole delay that need to corrected for proper phasing is divided into two parts:

a. Integral multiple of clock is implemented in course delay block.

b. Fractional delay is implemented in fine delay fringe stop block.

The data rate at the output will be 4 channels of 8 bits at 200MHz.

3. <u>PFB (Polyphase Filter Block) block:</u> The polyphase filter bank implements a hamming window. The PFB is used to reduce spectral leakage and to increase signal to noise ratio. The data rate at the output will be 4 channels each of 18 bits at 200MHz.

4. <u>FFT (Fast Fourier Transform)</u>: The FFT block used is FFT Biplex Real 4x (real-sampled biplex FFT). This block computes the real-sampled Fast Fourier Transform using the biplex FFT algorithm to use a complex core to transform two real streams. The data rate of operation at FFT output is 36 bits each at 400MHz. One of the streams gives even channels while the other gives odd channels. Each channel consists of an 18 (fix 18\_17 format)bit real part and an 18 bit imaginary part.

5. <u>Fine delay fringe stop Block</u>: Fringe delay appears due to the down conversion of the RF signal to the baseband signal. The delay values are compensated for baseband signal but this give a drift in phase for RF signal. To compensate this drift in phase fringe stop is used. Using fine delay fringe stop block we can apply maximum 1 clock delay.

6. <u>Equalizer block</u>: This block scale down the amplitude of incoming from the channels by a given factor to avoid the over flow during correlation and integration. The scaling factor depends on the integration time and power level of the signal. This block casts the 36 bits input data into 8 bits data so that the bit growth during accumulation does not overflow 32 bits.

7. <u>Beamformer and Integration block</u>: The beamformer block in the design performs the squaring of voltage of a channel and adds it to the square of voltage from other antennas. Its working is explained in detail in section 3.2. The output is all the self-correlated data. This beamformer data is transmitted using 10GbE so that host PC can read the data and store it on a disk for further use.

8. <u>Integration time</u> = (No. of FFT cycle)\*(No of FFT point)/(clock frequency)

9. <u>Data rate</u>= packet size/integration time.

# **4.2 BEAMFORMER SUBSYSTEM FLOWCHART**

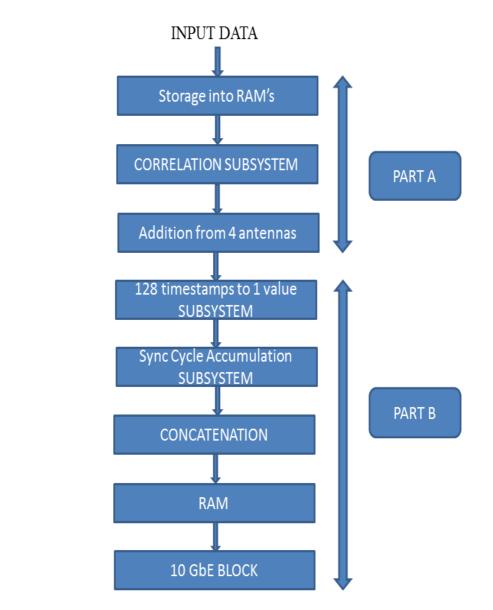

Figure 4.2 illustrates the signal flow of the beamformer subsystem.

The flow diagram is divided into 2 parts : PART A & PART B

Figure 4.2: Flowchart of Beamformer Subsystem

# **4.3.BEAMFORMER SUBSYSTEM DOCUMENTATION**

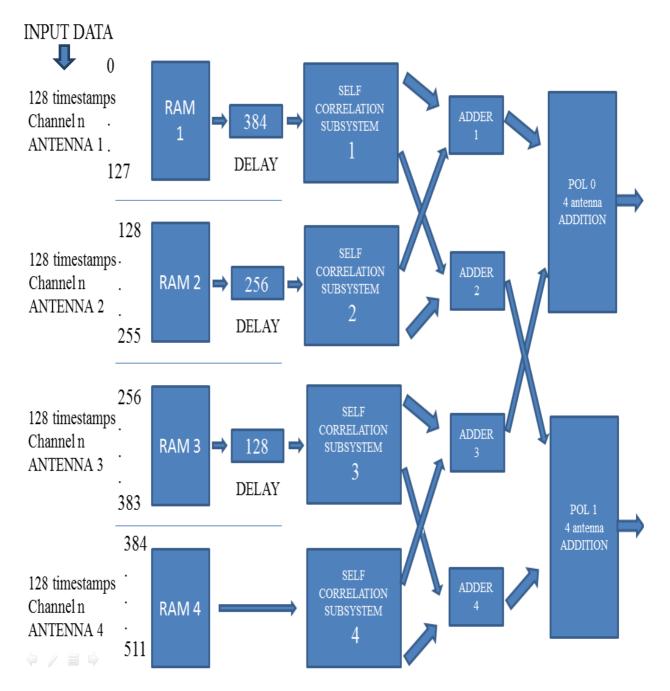

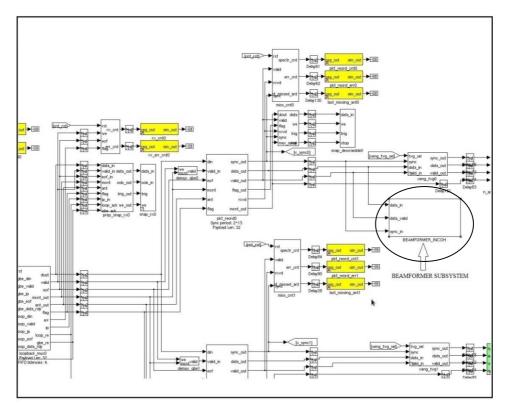

Figure 4.3 shows the block diagram of BEAMFORMER\_INCOH subsystem:

PART A:

Figure 4.3 Block diagram of Beamformer Subsystem:Part A

#### BLOCK DIAGRAM

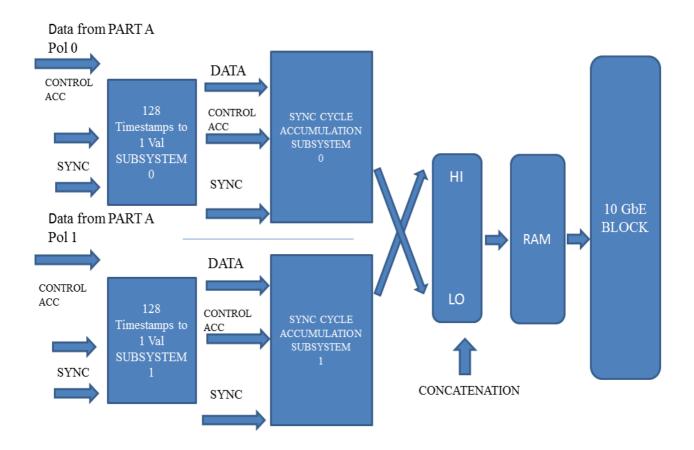

#### PART B:

Figure 4.4 Beamformer Subsystem Block Diagram: Part B

#### 4.3.1. INPUT TO THE SUBSYSTEM:

Figure 4.5 Position of the Incoherent Beamformer subsystem in the Packetized Correlator Design

The Beamformer subsystem comes after the Packet reorder block. Packet reorder block is the first part of an X-engine. It functions in the following manner:

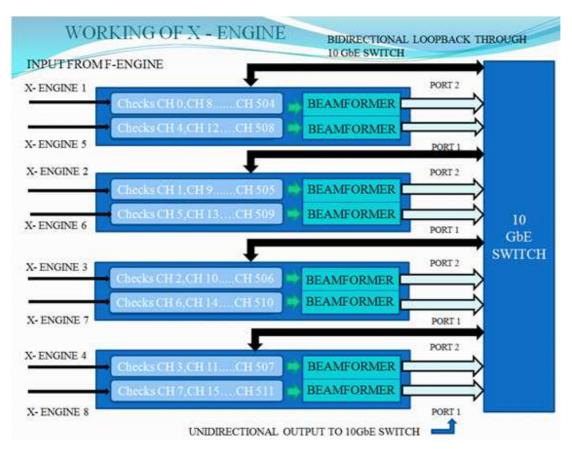

The input signal is given to the roach boards acting as the F engine. The signal initially goes through an ADC and then an FFT is taken. The data from 512 channels of the F- engine is passed on to the X- engine.

All 512 channels are not processed by a single X- engine but in fact are distributed among the 8 X-engines of the system. Each X-engine takes responsibility for processing only a certain number of channels. 512 channels distributed among 8 engines implies that each X-engine processes 64 channels individually. This means every 8 th channel is processed by the same X-engine.

For eg. X engine 1: processes Channel 0, Channel 8, Channel 16.....Channel 504.

X engine 2: processes Channel 1, Channel 9, Channel 17.....Channel 505.

X engine 3: processes Channel 2, Channel 10, Channel 18.....Channel 506.

X engine 4: processes Channel 3, Channel 11, Channel 19.....Channel 507.

X engine 5: processes Channel 4, Channel 12, Channel 20.....Channel 508.

X engine 6: processes Channel 5, Channel 13, Channel 21.....Channel 509.

X engine 7: processes Channel 6, Channel 14, Channel 22.....Channel 510.

X engine 8: processes Channel 7, Channel 15, Channel 23.....Channel 511.

Each X-engine processes only it's own set of channels irrespective of the antenna that the input is coming from.

There is a checker within each X-engine which checks if the incoming channel belongs to it's own set of channels. If it does belong then the X- engine accepts the data and passes it on to the beamformer subsystem for further processing.

If the incoming channel does not belong to it's own set of channels it does not accept the data and instead sends it to the 10 Gbe switch which routes it to the correct X- engine.

Figure 4.6 Working of first part of X-engine

The inputs to the beamformer subsystem are the following three signals:

- 1. Data\_valid signal: Boolean signal; when high the incoming data at the input data port is valid.

- 2. Sync signal: For synchronization between different X-engines.

- 3. Input data: 16 bit data.

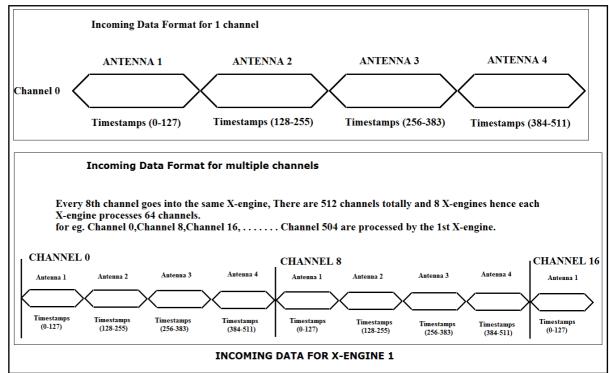

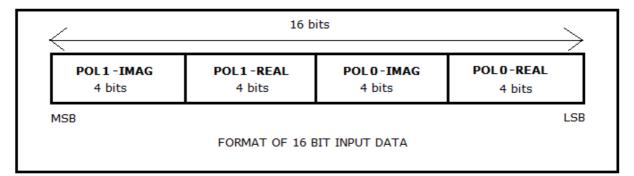

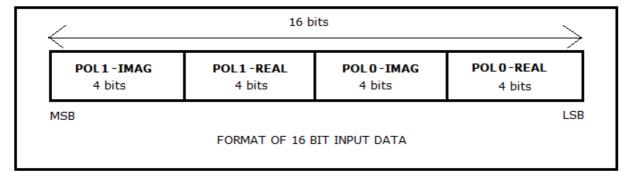

The input data comes in the following format:

Figure 4.7 Incoming Data format at the input data port for X-engine1

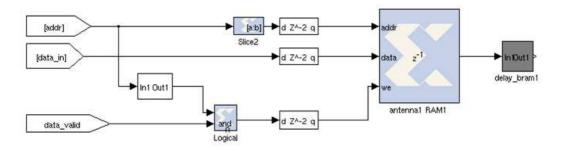

### 4.3.2. WRITIG THE DATA TO RAM

Figure 4.8 Writing Data to the RAM

1. <u>Antenna and corresponding RAM</u>: The incoming data is written to four single port RAMs. Each of these RAMs is 16 bit wide and has 128 address locations. Each one of these RAMs represents the corresponding antenna to which the data belongs. It is as follows.

| NUMBER OF ANTENNA FROM WHICH | THE RAM TO WHICH THE DATA IS |

|------------------------------|------------------------------|

| THE DATA IS COMING           | STORED                       |

| Antenna 1                    | RAM 1                        |

| Antenna 2                    | RAM 2                        |

| Antenna 3                    | RAM 3                        |

| Antenna 4                    | RAM 4                        |

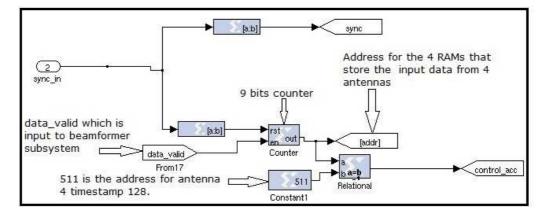

2. <u>Generating address for RAM</u>: A 9 bit counter gives the address. Only the 7 LSB are used to generate the address for a particular RAM. The 2 MSB are used for generating write enable which is explained in the next point. This counter has reset and enable ports. The counter is reset at every sync and it is enabled only when the data valid signal goes high.

3.<u>Generating the write enable signal for RAM</u>: One RAM has to be selected based on to which antenna the incoming data belongs to. This is done by using the 2 msb. Based on one them output of the selection block for only one BRAM is made high.

| VALUE OF TWO MSB OF THE ADDRESS | THE RAM SELECTED |

|---------------------------------|------------------|

| 00                              | RAM 1            |

| 01                              | RAM 2            |

| 10                              | RAM 3            |

| 11                              | RAM 4            |

Then this output and data\_valid are ANDed together and that is given to the write enable of that particular RAM.

4.<u>Input data:</u> The data comes as 128 time stamps for one channel from each antenna. This data is written into the single port RAM whose write enable is high.

#### 4.3.3 DELAY SECTION:

1. <u>Need</u>: As seen earlier (in Section 4.3.1)the format in which the incoming data arrives at the data input port of the beamformer subsystem. The data from antenna 1 arrives first and this is followed by data from antennas 2, 3 and 4 sequentially. There are 128 timestamps of data from each antenna. So data for antenna 2 timestamp 1 comes 128 clock cycles after that of antenna 1 time stamp 1. As the data comes sequentially, data for antenna 3 timestamp 1 comes 256 clock cycles after that of antenna 1 time stamp 1 and data for antenna 4 timestamp 1 comes 384 clock cycles after that of antenna 1 time stamp 1. In order that the data from all the antennas arrives at the same time for the next step of processing these delays are used.

2. <u>Implementation</u>: The timestamps from all antennas are made to arrive with the timestamps from antenna4 by delaying them. In order to provide these delays 3 separate delay blocks are used for antenna 1, 2 and 3. The data from antenna 4 is not delayed.

| ANTENNA NUMBER | DELAYED BY |

|----------------|------------|

| Antenna 1      | 384        |

| Antenna 2      | 256        |

| Antenna 3      | 128        |

The delay\_bram block from the CASPER DSP Block set is used here as the delay block

#### 4.3.4. SELF-CORRELATION

This is done separately for each antenna. Therefore we have four correlation subsystems used in the design.

1. <u>Separation of 16 bit input data</u>: The 16 bits of input data contain data for both polarizations. The bottom 8 bits consist of data for polarization 0 and the top 8 bits consist of data for polarization 1. These 8 bits are contain of real and imaginary parts of the data as can be seen from the figure bellow.

| Figure 4.9 | Format of     | input | data |

|------------|---------------|-------|------|

| 115010 4.7 | I officiation | mput  | uutu |

The separation of 16 bits data of the 128 time stamps is done sequentially. The 16 bit data is separated using **slice block** from the Xilinx simulink library. The processing of the two polarization has been done separately and in parallel here onwards.

2.<u>Squaring and Adding</u>: As it is an imaginary number, the square of an imaginary number is done as follows:

$(a+ib)(a-ib)*=a^2+b^2$ . We have used the multiplication block mult from the Xilinx simulink library for squaring and AddSub block from the Xilinx simulink library for addition. For a particular antenna, 128 time stamps are squared and added sequentially.

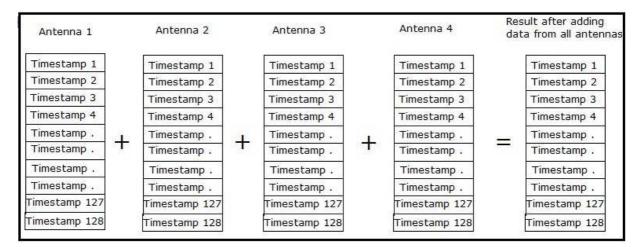

#### 4.3.5. ADDING DATA FROM ALL 4 ANTENNAS

For each antenna 2 outputs come out of the correlator subsystem. One is for polarization 0 and the other one is for polarization 2. Each of them gives out 128 timestamps of correlated data sequentially.

Now, the data from all the four antennas is added together.**AddSub** block from the Xilinx simulink library for addition. The figure 4.8 illustrates the addition.

Figure 4.10 Adding data from all antenna

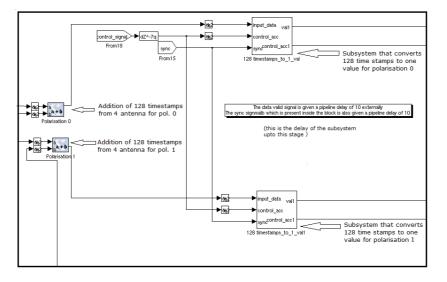

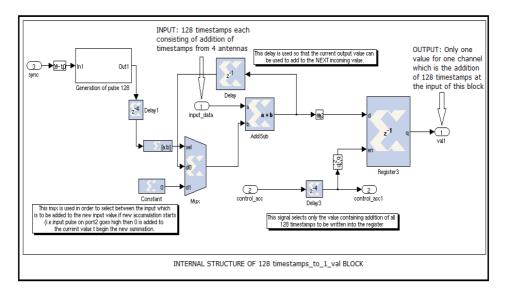

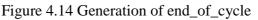

#### 4.3.6. CREATING ONE VALUE OF 128 TIME STAMP VALUES

The subsystem 128 timestamp\_to\_1\_val subsystem does this operation.

1.Input to this subsystem: The following 3 signals are the input to this system.

- 1. 128 timestamp data that comes sequentially at the input.

- 2. The sync signal that comes as an input to the Beamformer subsystem.

- 3. The control\_acc signal generated.

#### 2. <u>Generation of control\_acc signal</u>:

This signal has been derived inside the subsystem. This signal goes high every time when timestamp 128 from antenna 4 for every channel arrives at the input. (i.e. when all 512 timestamps which represent 1 channel have arrived at the input.)

This signal is generated as follows:

Figure 4.12 Generation of control\_acc signal

3.<u>Internal Structure of 128 timestamp\_to\_1\_val subsystem:</u>

Figure 4.13 Internal structure of 128 timestamps\_to\_1\_val block.

1) <u>Logic Used</u>: The addition of 128 timestamps gives us the value for 1 channel. But next time when 128 timestamps come at the input they belong to a different channel. So a new addition has to begin after 128 time stamps belonging to one channel have been added.

A multiplexer has been used for to serve this purpose. After every 128 clock cycles, 0 is selected as the second input to the adder. First input to the adder is the incoming timestamp data.

If the incoming time stamp data belongs to the same channel then the adders output of previous cycle is used as a second input to the adder.

#### 2) Generation of pulse signal of period 128 clock cycle:

<u>Where is it used</u>: This signal is used as a select signal to the multiplexer **Mux**, which selects between 0 and the previous output of the adder, to be the second input to the adder.

Why period of 128?: A period of 128 is selected as we want to add 128 timestamps.

3) <u>Use of register</u>: At the output of this subsystem we need only one value and that value should be addition of all correlated 128 timestamp values.

At the output of the adder at every clock cycle we have addition of the time stamps. But only at one particular cycle the output of the adder will have the addition of all correlated 128 timestamps. It is this value we desire. Whenever the control\_acc signal goes high we have this value at the output of the adder.

Hence, we have connected control\_acc signal to the enable port of the register so that only the desired value is passed to the next stages.

Register used here is the **Xilinx Register** from Xilinx Blockset and the multiplexer used is **Xylinx Bus Multiplexer** from Xilinx Blockset

3.<u>Outputs of this subsystem</u>: The two outputs of this subsystem are the val1 and control \_acc1 signal. Val1 is the value that is obtained by adding all the 128 timestamps of that particular channel. i.e. val1 is the channel value. control\_acc1 is just the control\_acc signal delayed by 4.

#### 4.3.7. Accumulation of Sync cycles:

Sync cycle\_accumulation subsystem is used for this purpose. This block is used to integrate multiple number of Sync cycles so as to obtain an averaged value of the incoming data.

The 3 inputs coming into the subsystem are:

- 1. DATA\_INPUT

- 2. CONTROL\_ACC

- 3. SYNC

The outputs coming out of the subsystem are:

- 1. INTEGRATED\_CHANNEL\_DATA

- 2. TX\_VALID

- 3. END\_OF\_FRAME

The position of this subsystem in the design of the beamformer subsystem is as shown in the following diagram.

\*\*Position in the flow of design

We have divided the subsystem into 3 main parts in order to explain the flow of the design through it.

| indicates one of the 3 input signals into the block.                                    |

|-----------------------------------------------------------------------------------------|

| indicates one of the output signals out of the block.                                   |

| indicates a FROM block so as to pass intermediary signals. These act as input signals.  |

| indicates a GOTO block so as to pass intermediary signals. These act as output signals. |

| LEGEND                                                                                  |

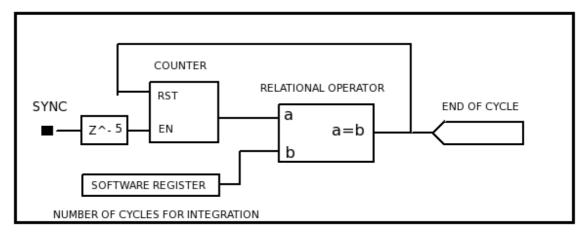

### 1. Generation of end of cycle signal:

This part depends on sync signal.

A variable "number of cycle for integration" is provided by the user through a software register so as to specify the number of cycles for which we want to integrate the channel data. It is configured through the Python script.

Let us say the value in the software register is given as n.

The Sync signal is used to enable a counter, when the value of this counter equals the "number of cycles for integration" provided in the software register we get a high pulse. This high pulse indicates that n cycles have been integrated. Thus this high pulse signal is called to the "end of cycle" signal. This signal is also used to reset the counter so that the counting for next cycle can begin.

# 2. <u>Generation of new-accumulation,tx-valid,end of frame and we-accumulator signals:</u>

This part depends on control\_acc and the end of cycle signals.

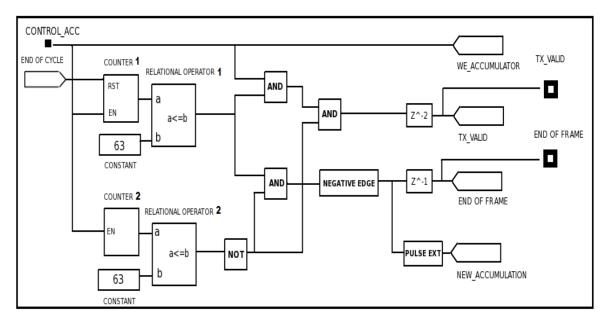

Figure 4.15 Generation of Tx\_valid and end of frame

#### Generation of these signals:

Counter 1 is enabled by the "CONTROL\_ACC" signal & reset by the "End of cycle" signal that was obtained in the first system. The output of this counter is given to Relational Operator 1. Relational Operator 1 compares this value with 63, as long as this value is less or equal to 63 we get a high pulse.

Counter 2 has only an Enable & no reset & even this counter is enabled by using the "CONTROL\_ACC" signal. The output of this counter is given to Relational Operator 1. Relational Operator 1 compares this value with 63, as long as this value is less or equal to 63 we get a high pulse.

The ouput of Relational Operator 2 is inverted. This inverted output is AND'ed with the output of Relational Operator 1. The output of this AND gate is given to a negative edge block. The output of this block is our "End of Frame signal". The output of this negative edge block is given to a PULSE EXTENDER block. This output of this block is passed ahead to the "New\_Accumulation" signal.

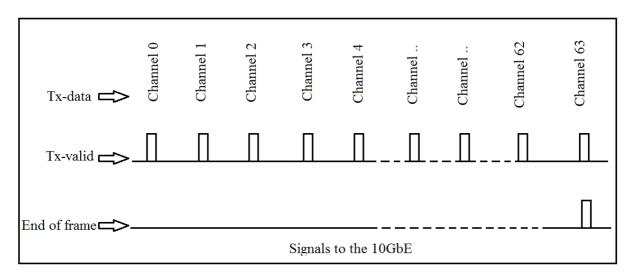

The output of Relational Operator 1 is AND'ed with the "CONTROL\_ACC" signal and the output of this AND gate is AND'ed with the inverted output of Relational Operator 2 mentioned earlier. This is our "TX\_VALID" signal.

#### Use of these signals:

<u>We-accumulator</u>: This signal is nothing but the control\_acc signal that comes into the 2^15 cycle accumulator subsystem. This signal is used as a write enable signal for PORT A and PORT B of the dual port RAM. There is delay difference between enable of port A and port B.

<u>New-accumulation</u>: This signal is the select signal to the Mux before the adder in the part 3 of this subsystem. This signal stays high for the entire duration of cycle 1 of every n cycle integration. After that it stays low till the integration of n cycles is completed.

<u>Tx-valid</u>: The "TX\_VALID" signal is very important for transmission over 10GbE. When this signal is high the core of the 10GbE accepts the data into the buffer. So, in our case every time addition of n cycles of channel values of the comes out of the PORTA of the dual port RAM, this signal goes high. That is, it is only in the last cycle that is nth cycle that we have the values that we want to transmit to the 10GbE block.

End of Frame: The "End of Frame" is a very important signal from the point of view of 10GbE. The End of Frame signal should go high when the last data of that particular packet comes to the data input port of the 10GbE. So, in our case when addition of n cycles of channel number 63 data values values comes out of the PORT A of the dual port RAM, this signal goes high That is, it is only in the last cycle, that is nth cycle, that we channel number 63 data comes out of port A this signal goes high

When the "End of Frame" signal is received, the packet of data get transmitted over the Ethernet. "End of frame" signals the transceiver to begin transmitting the buffered frame.

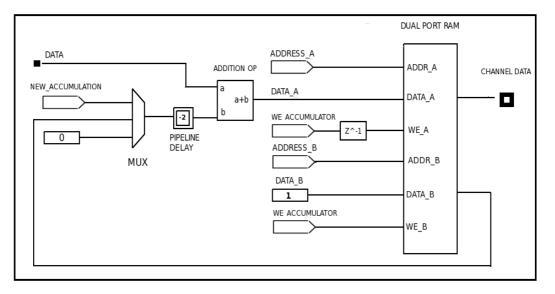

### 3. <u>Integration of multiple 2^15 cycles.</u>

We have used a Dual port RAM for carrying out the integration of multiple cycles. This dual port RAM is 32 bit wide and has 64 address locations.

This part is further divided into 2 parts.

#### 1) Address Generation for Port A and Port B.

This depends on both SYNC as well as CONTROL\_ACC

A Dual Port has 2 output ports A & B and requires 6 signals at it's input.

ADDR\_A(Address location for Data in Port A), DIN\_A(Input data for Port A), WE\_A(When this signal is high the Data pointed by DIN\_A is written into the address pointed by ADDR\_A), similarly it also possesses ADDR\_B, DIN\_B, WE\_B. These are for writing into Port B.

Figure 4.16 Generation of address for dual port RAM.

The ADDR\_A is generated by a counter which is reset by SYNC signal & enabled by the "CONTROL\_ACC" signal. Delays are adjusted accordingly. ADDR\_B is then derived from ADDR\_A as shown in the above figure.

The depth of the RAM used is 64.

We require ADDR\_B to be differing from ADDR\_A by the value 1. When ADDR\_A is 0, ADDR\_B is 1. When ADDR\_A is 1, ADDR\_B is 2 and so on. When ADDR\_A goes to 63 ADDR\_B goes to 0(63+1=64(1000000)) in 6 bits (000000)). The addition operation is done by an adder which uses wrap around mode in order to give us the above result. The following table illustrates the same.

| ADDRESS OF PORT A (ADDR_A) | ADDRESS OF PORT B (ADDR_B) |

|----------------------------|----------------------------|

| 0                          | 1                          |

| 1                          | 2                          |

| 2                          | 3                          |

|                            |                            |

|                            |                            |

|                            |                            |

| 63                         | 0                          |

### 2) Actual Integration done in dual port RAM:

This part needs the following signals:

Data Input Signal,we\_acc,new\_acc,addr\_a,addr\_b.

Figure 4.17 Accumulation using Dual Port RAM.

The NEW\_ACCUMULATION that was obtained in the  $2^{nd}$  system is used as a Select signal for a MUX to choose between the output of Port B and a constant of Value 0.The logic used for integration is as follows:

Let us consider the integration of first n cycles.

Suppose in Cycle 1 the data for 64 channels comes into the system & in the next cycle i.e. Cycle 2 a completely new set of data for 64 channels came into the system. Subsequently in Cycle 3 the system receives a third set of data for 64 channels and so on till the *n*th cycle. We want the output of our system to be the addition of these *n* cycles. This can be accomplished as follows.

At the start of cycle 1 the "NEW\_ACCUMULATION" signal selects the constant value 0 (input at port 1 of MUX) and this goes to the second input of adder for the addition operation. The data keeps streaming into the first input of the adder for the addition operation. Since the value at second input is 0 the value at first input of adder gets added by 0 only and hence moves to the output of the Addition operation without a change. This data is directly written to the PORT A of the DUAL PORT RAM. This "NEW\_ACCUMULATION" stays high for all the channels for every 1st cycle of integration.

As was defined earlier the address at PORT B of the DUAL PORT RAM differs from address at PORT A of the DUAL PORT RAM by 1. At the end of first cycle addr\_b will be pointing to address0 of the dual port RAM and addr\_a will be pointing to address 63.

Let us now consider the start of  $2^{nd}$  cycle:

The "NEW\_ACCUMULATION" signal is designed that it now selects the value at Port 0 of the MUX. This is actually the output of Port B from the RAM. Earlier addr\_B was pointing to address 0 then at the port B output contains the data for channel 0.Now this value moves on to the second input of the addition operation block. While at the second input of the adder we have the 2<sup>nd</sup> cycles input data for channel 0.These 2 values get added by the Addition Operation Block & moves onto the input at DATA\_A.

Thus in general it can be summarized as, the value of a certain channel at the first input of the Addition operation block is it's value in the  $2^{nd}$  cycle & the value of in  $1^{st}$  cycle comes at second input of the Addition operation block. Now in the  $3^{rd}$  cycle, the addition of the values of the  $1^{st}$  &  $2^{nd}$  cycle get added to the now incoming data of the  $3^{rd}$  cycle, in the *n*th cycle the value at second input of the adder is the addition of all the previous cycles of that channel and at the first input of the adder the incoming data is the value of that channel in the *n*th cycle.

This can be done for any number of cycles that the user wants to integrate.

Once this number has been reached, the Output of the Dual Port RAM contains values that are to be sent forward to the Packetization stage.

NOTE: This sync cycle accumulator works perfectly for 1 cycle of integration i.e. base integration. But for greater number of integrations there are some unexpected drops in the output. These have been removed using the logic of the on-board integrator given in the Add-on section(Chapter 9) of this report.

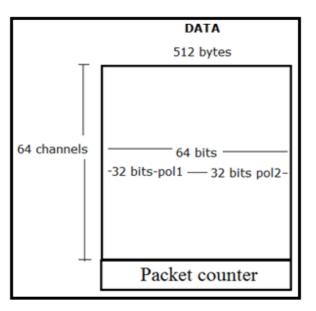

### 4.3.8. PACKETIZATION STAGE:

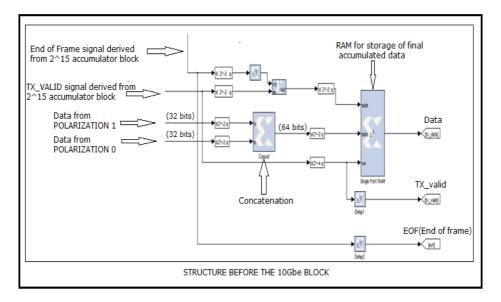

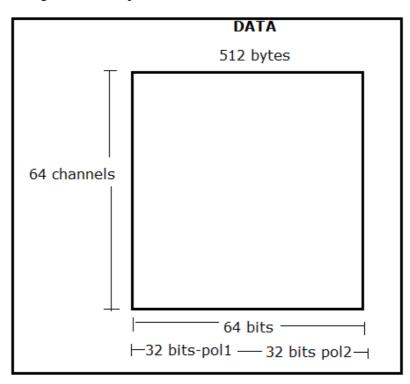

1) <u>Requirements of 10GbE block</u>: We have input data in the form of 16 bits which contains information from Polarization 0 and Polarization 1. This data gets split into the respective Polarizations and independent parallel processing takes place till this stage. At the Packetization

stage the data is packetized according to the requirements of the 10GbE NIC. The 10GbE block accepts only a 64 bit wide data stream with user-determined frame breaks.

2) Formation of 64 bits wide data: The data from both polarizations is 32 bit wide. Both polarizations are concatenated to form a width of 64 bits. Then this 64 bits wide data is stored in a Single port RAM before sending it to the 10GbE block. Then 10GbE block wraps this data stream in a UDP frame for transmission. The block used for concatenation is the **Concat** block from Xilinx blockset in the Simulink library.

Figure 4.18 Temporary storage before 10GbE block.

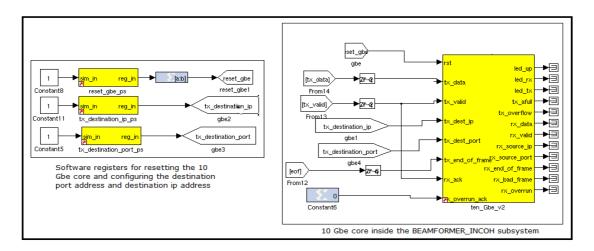

3)<u>The 10GbE setup</u>: The 10GbE block requires inputs as data, reset, tx\_valid, tx\_dest\_ip, tx\_dest\_port,tx\_end\_of\_frame. Out of these tx\_end of frame, tx\_valid and tx\_data are generated inside the BEAMFORMER\_INCOH subsystem.

For the reset, tx\_dest\_ip and tx\_dest\_port software registers are present in the design. These software registers are configured via a python script. The following diagram shows the 10GbE setup within the design. The 10GbE block used is the **ten\_Gbe\_v2** block from the BEE\_XPS System Blockset in the Simulink library.

Figure 4.19 10GbE setup in the design.

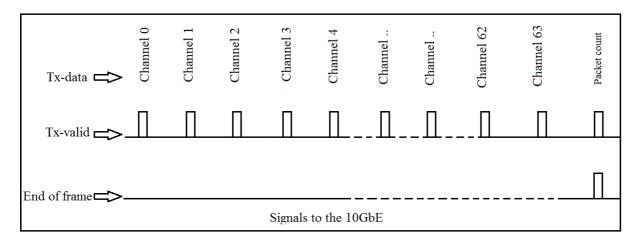

Figure 4.18 shows the signals that are given to the 10 GbE block and the relationship between them.

Figure 4.20 Signals to the 10GbE.

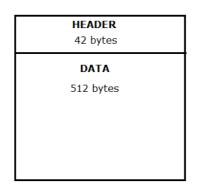

4)<u>UDP packet</u>: The 10GbE block sends a out a UDP Packet. Packet Format that is transmitted over 10GbE is as follows:

Figure 4.21 UDP packet

And the data in the UDP packet is as shown in figure 4.20 :

|            | POLARIZATION 1 (32 bits)    | POLARIZATION 2 (32 bits)    |

|------------|-----------------------------|-----------------------------|

|            | 64 1                        | BITS                        |

| CHANNEL 0  | (V1)^2+(V2)^2+(V3)^2+(V4)^2 | (V1)^2+(V2)^2+(V3)^2+(V4)^2 |

| CHANNEL 1  | (V1)^2+(V2)^2+(V3)^2+(V4)^2 | (V1)^2+(V2)^2+(V3)^2+(V4)^2 |

| CHANNEL 2  | (V1)^2+(V2)^2+(V3)^2+(V4)^2 | (V1)^2+(V2)^2+(V3)^2+(V4)^2 |

|            |                             |                             |

|            |                             |                             |

|            |                             |                             |

|            |                             |                             |

|            |                             |                             |

|            |                             |                             |

| CHANNEL 62 | (V1)^2+(V2)^2+(V3)^2+(V4)^2 | (V1)^2+(V2)^2+(V3)^2+(V4)^2 |

|            | (V1)^2+(V2)^2+(V3)^2+(V4)^2 | {V1)^2+(V2)^2+(V3)^2+(V4)^2 |

| CHANNEL 63 |                             |                             |

|            | DATA IN THE                 | UDP PACKET                  |

Figure 4.22 Data in the UDP packet.

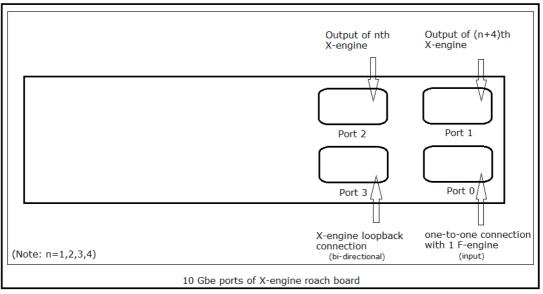

On a roach board, there are two X-engines; therefore there are two BEAMFORMER\_INCOH subsystems on a single roach board. The 10GbE for the upper subsystem gives the output at 10GbE port 2 of the roach board and the lower subsystem gives the output at 10GbE port1 of the roach board.

# 5. Calculations for Packetized Beamformer

## **5.1 NUMBER OF BITS CALCULATION:**

(<u>NOTE:</u> Where ever we say integration it refers to the 2^15 cycle accumulation.)

The following calculation is done for one polarization. The same is true for the next.

1)The 16 bits input data has the following content in it.

We separate the real and imaginary parts of each polarization.

2) Then,

For each timestamp we do the following:

#### $R^2+I^2$ .

Now the real part consists of 4 bits and the imaginary part consists of 4 bits.

So, the maximum value for each one of them will be:

R<sub>max</sub>=1111, I<sub>max</sub>=1111.

That is  $R_{max=} I_{max} = 16$ .

3) Now we have to square each one of them:

So, it will be:  $(R_{max})^2 = (I_{max})^2 = 256$ .

Therefore the number of bits required to represent this maximum value will be 8 bits.

4) Now in the next step we have to add the real part square and the imaginary part square.

So, ( (  $R_{max}$ )<sup>2</sup>+( $I_{max}$ )<sup>2</sup>)=256+256=512.

Therefore the number of bits required to represent this maximum value will be 9 bits.

5) In the next stage we have to add all 128 timestamps value and make one value out of them.

So, if all the 128 time stamp values have maximum value then the value of addition will be:

128\*( (  $R_{max}$ )<sup>2</sup>+(  $I_{max}$ )<sup>2</sup>)= 128\*512=65536.

Therefore the number of bits required to represent this maximum value will be 16 bits.

This value represents the value for 1 channel without integration.

# Therefore 16 bits would be enough to represent the channel data values without integration.

The same is true for other polarization.

# **5.2 NUMBER OF INTEGRATION CYCLES:**

From the above calculation, we know that the maximum value for 1 channel can be represented in 16 bits.

But we are using 32 bits for representing the channel data for one polarization.

Therefore the maximum number of integrations that can be done are :

$(2^{32}) \div (2^{16}) = 2^{16}$ .

Therefore we conclude that the maximum number of integrations that we can do is  $2^{16}$ =65536.

(NOTE: Following calculations have been done for 1 X-engine.)

# **5.3 INTEGRATION TIME CALCULATION:**

In one sync cycle, we have 128 time samples for each channel are received from 4 antennas. In one sync cycle 64 channels are received by one X engine.

Therefore we need 128\*4\*64 = 32768 clock cycles.

The operating frequency of ROACH board is 200 MHz .Therefore, one clock cycle time period is 5nanosecond.Total time for one sync cycle to be completed = 32768 \*5ns =0.163millisecond(163 microseconds.)

If integrate further, then for 10 cycles the time taken would be 163 microsecond \*10(1.63 milliseconds.)

GMRT-TIFR

These values have been verified with the wireshark software . As a packet is sent out after the specified numbers of integration cycles have been completed.

The following image is a wireshark snapshot for base integration. The leftmost column displays the time at which the packet arrives from the X-engine.

| 0            | Time                                       | Source                                                                                    | Destination          | Protocol     | Info                                       |

|--------------|--------------------------------------------|-------------------------------------------------------------------------------------------|----------------------|--------------|--------------------------------------------|

|              | 1 0.000000                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 3            | 2 0.000166                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

|              | 3 0.000328                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

|              | 4 0.000491                                 | 192.168.8.201                                                                             | 192.160.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 5 0.000657                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 6 0.000819                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 3            | 7 0.000986                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 8 0.001149                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| )            | 9 0.001312                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 0 0.001476                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 1 0.001640                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 2 0.001804                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 1            | 3 0.001966                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| 14           | 4 0.002129                                 | 192.168.8.201                                                                             | 192.168.8.200        | UDP          | Source port: 60000 Destination port: 60000 |

| Fram<br>Ethe | e 1 (554 bytes on w<br>rnet II, Src: MS-NL | vire, 554 bytes captured)<br>.B-PhysServer-02_c0:a8:08:c9<br>: 192.168.8.201 (192.168.8.2 | (02:02:c0:a8:08:c9), | Dst: Broadca | st (ff:ff:ff:ff:ff)                        |

It is 163 micrsecond s\*1(0.163milliseconds).

▷ User Datagram Protocol, Src Port: 60000 (60000), Dst Port: 60000 (60000)

▷ Data (512 bytes)

Figure 5.1 Wireshark snapshot for 1 integration cycle.

The following image is a wireshark snapshot for 2 integration cycles . The leftmost column displays the time at which the packet arrives from the X-engine.

It is 163 micrsecond s\*2=0.326milliseconds.

| No | Time     | Source        | Destination   | Protocol | Info                                       |

|----|----------|---------------|---------------|----------|--------------------------------------------|

| 1  | 0.000000 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 2  | 0.000326 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 3  | 0.000655 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 4  | 0.000983 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 5  | 0.001312 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 6  | 0.001636 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 7  | 0.001963 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 8  | 0.002366 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 9  | 0.002696 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 10 | 0.002947 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 11 | 0.003348 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 12 | 0.003638 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 13 | 0.003933 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 14 | 0.004255 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

Ethernet II, Src: MS-NLB-PhysServer-02 c0:a8:08:c9 (02:02:c0:a8:08:c9), Dst: Broadcast (ff:ff:ff:ff:ff:ff)

▷ User Datagram Protocol, Src Port: 60000 (60000), Dst Port: 60000 (60000)

Data (512 bytes)

Figure 5.2 Wireshark snapshot for 2 integration cycles.

<sup>▶</sup> Internet Protocol, Src: 192.168.8.201 (192.168.8.201), Dst: 192.168.8.200 (192.168.8.200)

The following image is a wireshark snapshot for 10 integration cycles . The leftmost column displays the time at which the packet arrives from the X-engine.

| No | Time       | Source        | Destination   | Protocol | Info                                       |

|----|------------|---------------|---------------|----------|--------------------------------------------|

|    | 1 0.000000 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 2 0.001692 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 3 0.003343 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 4 0.004981 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 5 0.006618 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 6 0.008257 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 7 0.009918 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 8 0.011537 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

|    | 9 0.013172 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 1  | 0 0.014785 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 1  | 1 0.016450 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 1  | 2 0.018088 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 1  | 3 0.019726 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

| 1  | 4 0.021366 | 192.168.8.201 | 192.168.8.200 | UDP      | Source port: 60000 Destination port: 60000 |

▷ Frame 1 (554 bytes on wire, 554 bytes captured)

Ethernet II, Src: MS-NLB-PhysServer-02 c0:a8:08:c9 (02:02:c0:a8:08:c9), Dst: Broadcast (ff:ff:ff:ff:ff:ff:ff)

Internet Protocol, Src: 192.168.8.201 (192.168.8.201), Dst: 192.168.8.200 (192.168.8.200)

▷ User Datagram Protocol, Src Port: 60000 (60000), Dst Port: 60000 (60000)

▷ Data (512 bytes)

Figure 5.3 Wireshark snapshot for 10 integration cycles

# **5.4 DATA RATE CALCULATION:**

The data that goes into one packet is as follows:

The minimum integration i.e. only 1 cycle of 2^15 is taken into consideration then every 0.163 millisecond (i.e. 163 microsecond), a packet is transmitted from the X-engine. The data packet that is sent over the 10Gbps has the following format:

There are two options for capturing the data packets via Gulp. One option is to capture with the header and another without header. We will be calculating the data rate for both the options:

#### 1) <u>Without header:</u>

Every 163 microsecond 1 packet of 512 bytes is sent out of one X-engine.

Therefore in 1 second 3.14 Mbytes are transferred.

Data Rate = 3.14 Mbytes \* 8 (to convert to bits per second)

=25.13 Mbps.

2) <u>With Header:</u>

Every 163 microsecond 1 packet of 554 bytes is sent out of one X-engine.

Therefore in 1 second 3.398 Mbytes are transferred.

Data Rate = 3.398 Mbytes \* 8 (to convert to bits per second)

=27.19 Mbps.

## 6. Depacketization and Post-Processing

### **6.1 DEPACKETIZATION:**

This stage further consists of two parts.

- 1. <u>Converting to ASCII</u>: The data packets captured by gulp are in binary format. These are converted into ASCII format. Further Polarization 1 and Polarisation 0 data is separated.

- 2. <u>Separating into 8 files</u>: Gulp captures packets that are sent over 10Gb Ethernet.8 Different roach Boards are transmitting packets over a single 10Gb Ethernet. Hence these received packets have to be separated depending on the X-engine to which has transmitted that particular packet.

#### **6.2 POST-PROCESSING:**

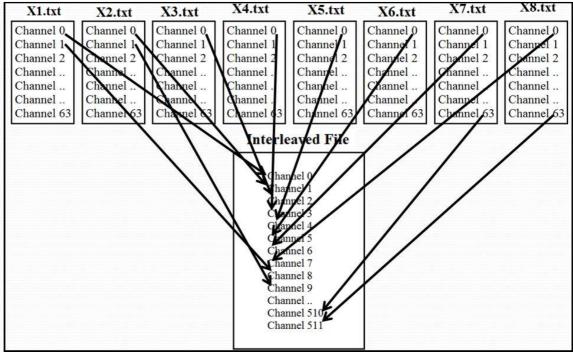

In post processing, the data received from all the 8 X-engines separately, has to be interleaved in a particular order so as to get the entire spectrum of 512 channels. Section 6.3 explains both the Separation into 8 files and interleaving in depth.

#### **6.3 LOGIC USED FOR SEPARATION AND INTERLEAVING:**

The Packetized Beamformer design described here has the following specifications:

- 1. Number of spectral channels: 512

- 2. Number of X-engines: 8

- 3. Number of channels processed by each X-engine: 64.

Each X-engine receives data of only those 64 channels which it has programmed to process. After processing this data, each X engine sends out a packet which contains the channel data of these 64 channels. These packets are sent over a single 10GbE connection.But the channels that each X-engine receives are not consecutive. They are in the following format (Table X).

| Sr. No. |           | Channel Numbers for each X-engine: |           |           |           |           |           |           |  |  |  |

|---------|-----------|------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|

|         | X-engine1 | X-engine2                          | X-engine3 | X-engine4 | X-engine5 | X-engine6 | X-engine7 | X-engine8 |  |  |  |

| 1       | 0         | 1                                  | 2         | 3         | 4         | 5         | 6         | 7         |  |  |  |

| 2       | 8         | 9                                  | 10        | 11        | 12        | 13        | 14        | 15        |  |  |  |

| 3       | 16        | 17                                 | 18        | 19        | 20        | 21        | 22        | 23        |  |  |  |

| •       |           |                                    |           |           |           |           |           |           |  |  |  |

| •       |           |                                    |           |           |           |           |           |           |  |  |  |

| 63      | 496       | 497                                | 498       | 499       | 500       | 501       | 502       | 503       |  |  |  |

| 64      | 504       | 505                                | 506       | 507       | 508       | 509       | 510       | 511       |  |  |  |

For processing the entire spectrum, we have to interleave the data of the 10GbE packets coming from each X-engine. Interleaving is carried out in 2 steps as follows.

- 1. The incoming data captured by gulp is separated into 8 files depending on the source IP of the X-engines.

- 2. The spectral channels from these 8 files have to be arranged serially.

These two things are achieved using the following technique :

Separating the data into 8 files (according to the X-engine): The data packets sent over the 10Gbe connection are UDP packets. Each of these packets contains a header of 42 bytes. This header contains the IP address of the source and destination in the 27<sup>th</sup> to 30<sup>th</sup> byte respectively.

The header structure is as follows:

|                                                                                   | Broadcast<br>(6 bytes) Address of phy. server<br>(2 bytes) |                   |     |                |                |                             |                             |

|-----------------------------------------------------------------------------------|------------------------------------------------------------|-------------------|-----|----------------|----------------|-----------------------------|-----------------------------|

| Address o<br>(4 b                                                                 | f phy. se<br>ytes)                                         | rver              |     | //             |                | ECN CE<br>(1 byte)          |                             |

| Total len.<br>(2 bytes)                                                           | Identifi<br>(2 byte                                        |                   | Fra | gment<br>(2 by | Offset<br>tes) | Time to<br>live<br>(1 byte) | Protocol<br>UDP<br>(1 byte) |

| Header<br>Checksum<br>(2 bytes)                                                   |                                                            | e IP a<br>4 bytes |     | ess            | Destin         | ation I                     | P address                   |

| Destination IP address Source port (2 bytes) Length (2 bytes) (2 bytes) (2 bytes) |                                                            |                   |     |                |                |                             |                             |

| Checksum<br>(2 bytes)                                                             |                                                            |                   |     |                |                |                             |                             |

Figure 6.1 UDP Packet Header

Each of the 8 X-engines uses a different IP address. So, the X-engine that is sending a particular packet can be identified on the basis of the source IP present in the packet header sent by it.

Gulp captures the packets along with the header. A utility is developed to extract the source IP from the header, identify it and accordingly select a file in which data has to be written. This utility also converts the packet data into GNU compatible and PMON compatible format. Thus 8 different files each containing data from a particular X-engine are created at the end of this process.

2. <u>Interleaving the 8 files to get a serial output:</u> Then these 8 files are provided to the interleaving code which arranges the channel data sequentially. Figure 6.2 illustrates how channels from 8 different files are arranged in a single file.

Figure 6.2 Interleaving

In the figure 6.2, X1.txt contains data from X-engine 1, X2.txt contains data from X-engine 2 and so on.

A "packet count" can be an add-on to the system. It will ensure interleaving of time synchronized packets.

3. <u>Ensuring time synchronized interleaving</u>: A packet counter can be transmitted along with the channel data. This is appended to the data packet at the packetization stage (before sending it over the 10 GbE link). This packet counter acts as a time stamp for synchronization of packet transmission from different X-engines. The process of interleaving starts with checking of the packet counter. Only the packets from different

X-engines containing same packet counter will be interleaved together. If even one X-engine's packet with a specific packet count is not received, then all the packets with that packet count from other X-engines will be discarded.

## 7. Packetized Beamformer Test Setup

#### 1) DESIGN SPECIFICATIONS:

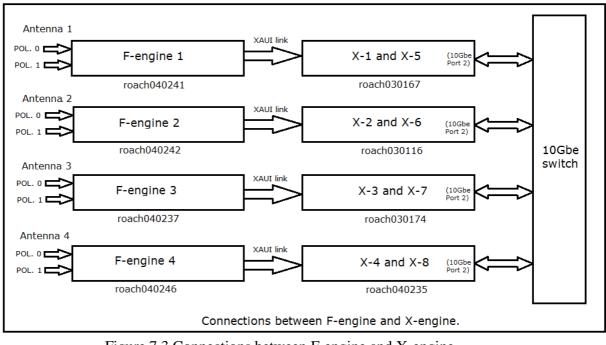

Number of F-engines: 4 Number of X-engines: 8

#### 2) ROACH BOARDS USED:

ROACH boards used as F-engine: ROACH040241, ROACH040242, ROACH040237, ROACH040246. ROACH boards used as X-engine: ROACH030167, ROACH030116, ROACH030174, ROACH040235.

There are two X-engines per ROACH board. The X-engines and the corresponding ROACH boards are as mentioned in the following table:

| ROACH BOARD NUMBER | CORRESPONDING X-ENGINES |

|--------------------|-------------------------|

| 030167             | X1 and X5               |

| 030116             | X2 and X6               |

| 030174             | X3 and X7               |

| 040235             | X2 and X8               |

Table (Y): ROACH board corresponding to the 8 X-engines.

(Note: Any other ROACH board can be used by providing the name of the desired ROACH board in the config\_4ant script. Also make changes in the server\_f and server\_x accordingly.)

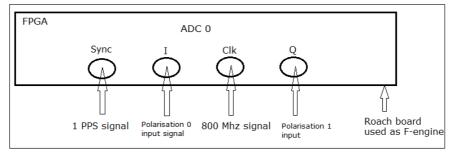

#### 3) CONNECTIONS TO THE F-ENGINE:

F-engine is given four inputs:

- 1) Sync

- 2) I (Polarisation 0 input)

- 3) Clock

- 4) Q (Polarisation 1 input)

Figure 7.1 Connections to F-engine.

#### 4) 10 GbE PORT CONNECTIONS OF X-ENGINE:

Every ROACH board has 4 10 GbE ports. The connections to them are as shown in the figure 7.2:

Figure 7.2 10GbE port connections of X-engine.

#### 5) CONNECTIONS BETWEEN F-ENGINE AND X-ENGINE:

The connections between F-engine and X-engine are as shown in the following diagram:

Figure 7.3 Connections between F-engine and X-engine

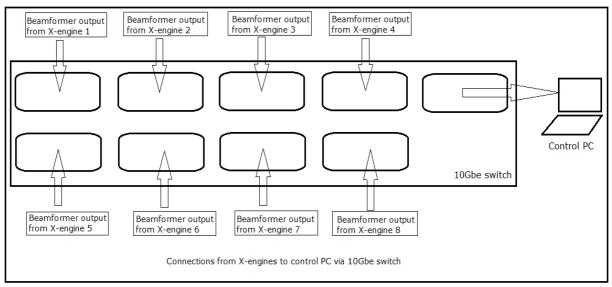

#### 6) CONNECTIONS FROM X-ENGINE TO CONTROL PC:

The connection from the X-engines to control PC is made via the 10GbE switch. The following diagram shows these connections.

Figure 7.4 Connections from X-engines to control PC via 10 GbE switch.

# 8. Testing of the Designs and Results

The BEAMFORMER\_INCOH subsystem was designed in the MATLAB software using the blocks of CASPER blockset and XYLINX blockset in the simulink library.

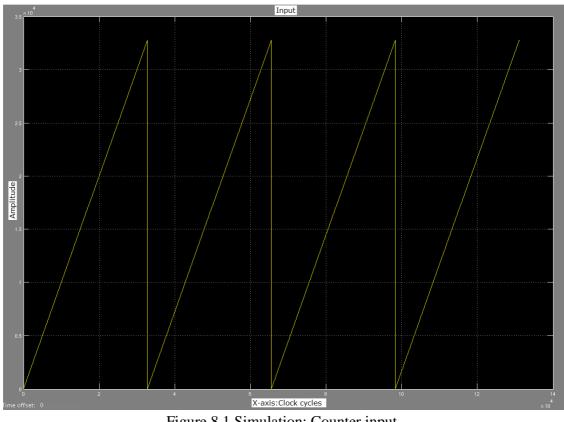

As the first step of testing, a 16 bit counter data was given as input to the BEAMFORMER\_INCOH subsystem and the results were verified by matching the results with theoreotical calculation. The simulation results are attached below.

#### **8.1 Simulation results**

Test parameters for the simulation carried out:

Input: 16 bit counter.

No. of cycles for which 2<sup>15</sup> accumulation is to be carried out: 3.

1) Input: The Figure 8.1 is the output of the 16 bit counter as given to the beamformer subsystem for 3 2^15 cycle. One ramp is considered as 128 timestamp data for all 64 channels in one sync cycle.

Figure 8.1 Simulation: Counter input

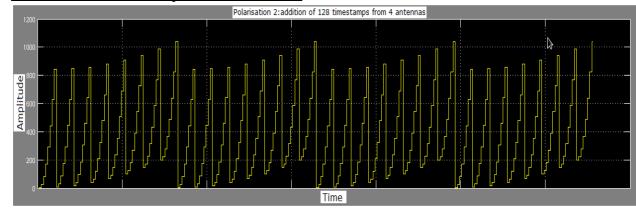

2) Addition of 128 timestamps from all antennas:

Figure 8.2 Simulation: Addition of 128 timestamps from all antennas.

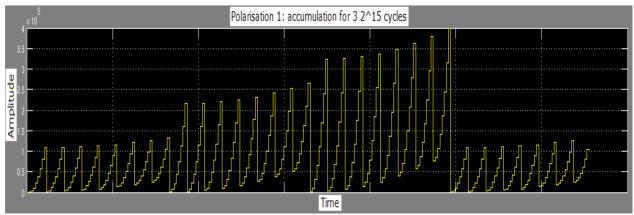

#### 3) <u>Output of 2^15 accumulator block:</u>

The accumulation takes place as follows. As our design is for accumulating 3 cycles of  $2^{15}$ , we can see that it adds the 3 cycles of  $2^{15}$  and after that it starts new accumulation.

Figure 8.3: Simulation: Output of accumulator block.

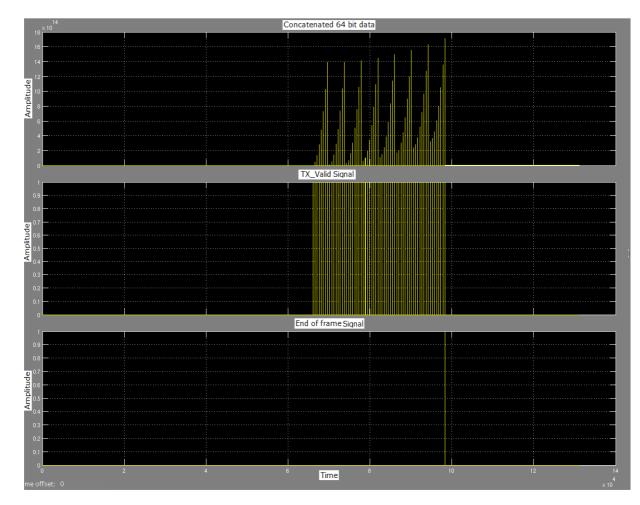

#### 4) <u>Generation of data,tx\_valid and eof for 10Gbe core:</u> (Refer Figure 8.4)

1.The 1st graph shows the the ouput data after concatenating the polarisation1 and polarization 0 data. Each signal corresponds to one channel data. They are 64 in number. 2. The 2nd graph shows the data transmission valid signal which is fed to Tx\_valid signal of the 10GbE NIC.

3. The  $3_{rd}$  signal shows the end of frame signal. After this signal goes from 1 to 0, the 10GbE NIC acknowledge it as a end of one packet.

Figure 8.4 Simulation: 10GbE signals.

#### **8.2 Sinewave test result**

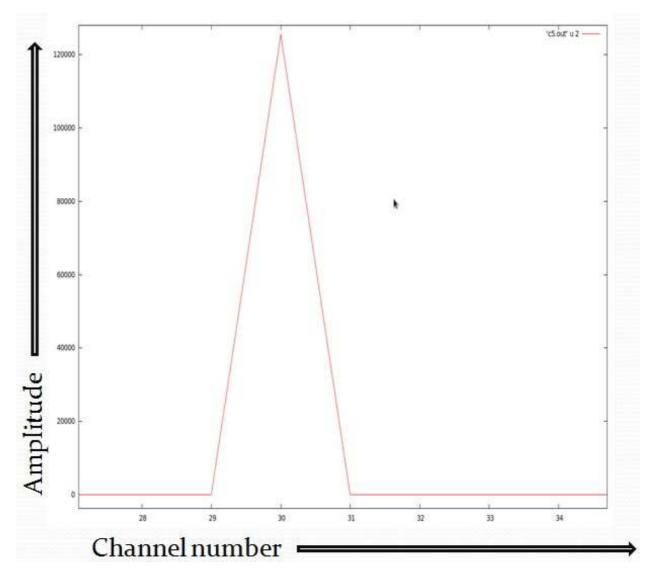

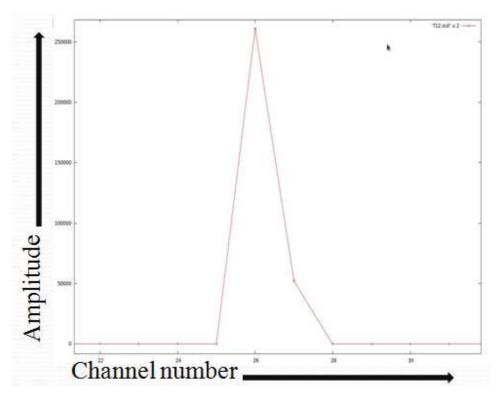

1.Sine wave test 1

Input: Sine wave at frequency 187.5 MHz

Roach board used: roach030167 used as X-engine.

Expected output:

The frequency 187.5 MHz belongs to channel number 30 of this X-engine. A peak is expected in the output at channel number 30 .

Interpretation of the figure:

<u>X –axis</u>: Channel number

<u>Y-axis</u>: Amplitude

GMRT-TIFR

A peak is present at channel number 30. No where else a peak is present. This indicates that input signal contains frequency component corresponding to channel no.30 of this particular X-engine.

Figure 8.5: Sine wave test result 1

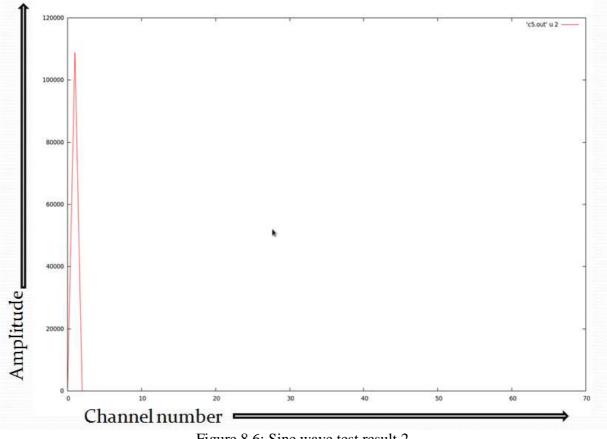

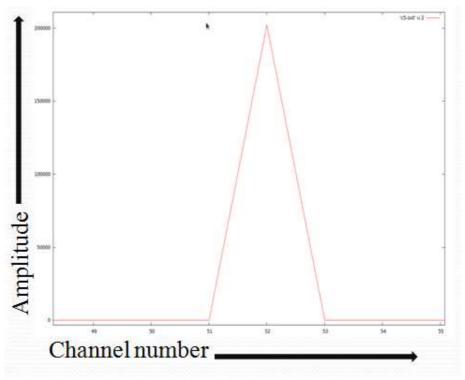

2.Sine wave test 2

Channel 8 in the 512 channel spectrum.

Frequency: 6.25 MHz

X-engine used: 1

X-engine channel no.:1

Figure 8.6: Sine wave test result 2

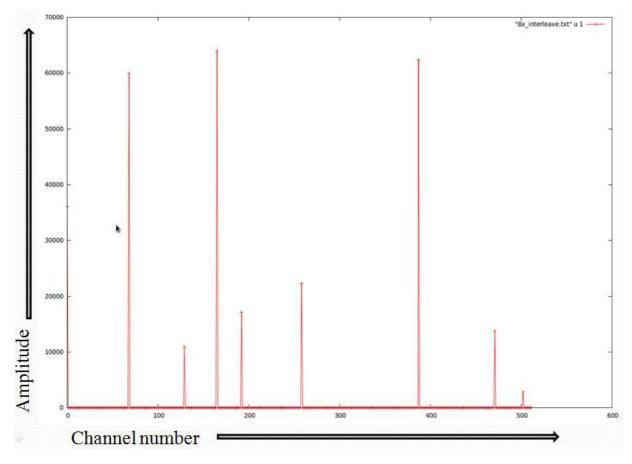

#### **8.3 Interleaved data from 8 X-engines:**

TEST : To check the functioning of interleaving code.

Connection:One to one connection between X-engine and control PC

Input: Sine wave frequencies belonging to each X-engines were given one by one as an input.

Processing: Data was captured separately and interleaved.

Output: Peaks observed at the respective channel numbers.

Figure 8.7: Interleaving result for 8 separate files.

#### 8.4 Role played by data\_valid

#### Sine wave without Data\_valid:

(Refer figure 8.8) The input and output both were shifted. Notice the peak in output. Input: Frequency:156.25 MHz Channel input: 25 Output channel:26(shifted)

Figure 8.8: Sinewave Output-Data\_valid not used.

### Sine wave output with Data\_valid:

(Refer figure 8.9)

The shifting is eliminated. Peak at exact location. Input Frequency:325 MHz Channel input: 52 Output channel:52 (not shifted)

Figure 8.9: Sinewave Output: Data\_valid used

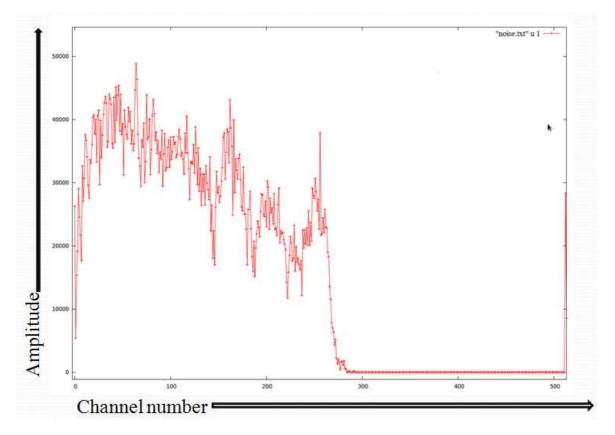

#### **8.5** Noise test results

Connections: All 8 X-engines connected to control PC via 10GbE switch

Input: Signal from noise generator passed through a low pass filter of 200 Mhz.

Output: GNU plot of the interleaved data from all X-engines

Figure 8.10. Noise Test Result-512 channel spectrum

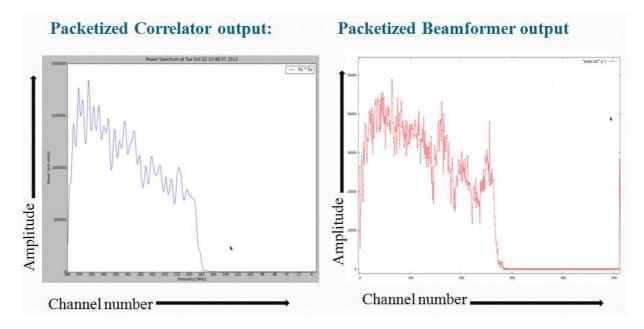

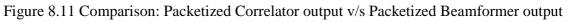

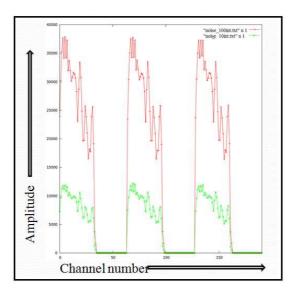

Comaprison: Output of packetized Correlator Output and packetized Beamformer for Noise test.

#### 8.6 Improvement in sensitivity with increase in number of antenna

Refer figure 8.12.

The colour code is as follows:

Pink- Noise output for input given to 1 antenna.

Blue- Noise output for input given to 2 antennas.

Green- Noise output for input given to 3 antennas.

Red- Noise output for input given to 4 antennas.

Figure 8.12. Noise test Output for Increasing Number of Antennas.

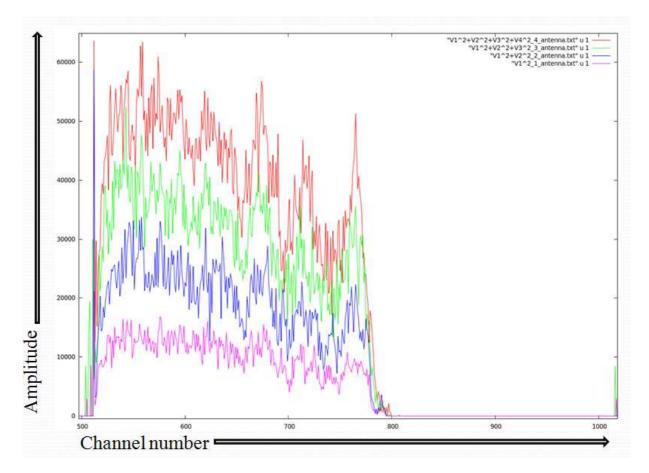

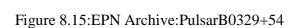

#### 8.7 Pulsar test:

1.TEST:

- <u>Date of observation</u>: 30<sup>th</sup> October 2013.

- <u>Pulsar</u>: B0329+54(Period: 714.578196 msec)

- <u>Antennas used</u>: 4 central square antennas used.

- <u>Sampling clock</u>: 800MHz.

- <u>Data acquisition</u>: 5mins

- <u>Integration time</u>: 0.164 millisecond

- <u>Beamformer Bandwidth</u>: 400 MHz

- <u>RF Bandwidth</u>: 32 MHz

- <u>Number of channels</u>:512

Figure 8.13 PMON Profile for Pulsar B0329+54

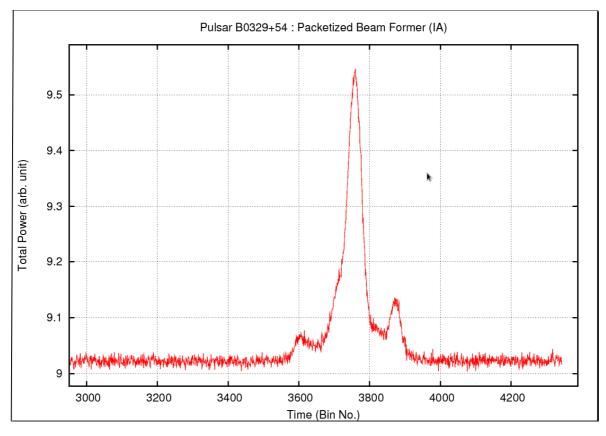

# COMPARING PULSAR RESULT WITH THEOREOTICAL RESULT: Pulsar B0329+54

### **GSB** Output

EPN Data Archive

.610 GHz

Figure 8.14:GSB output:Pulsar B0329+54

180

200

160

### PACKETIZED BEAMFORMER OUTPUT

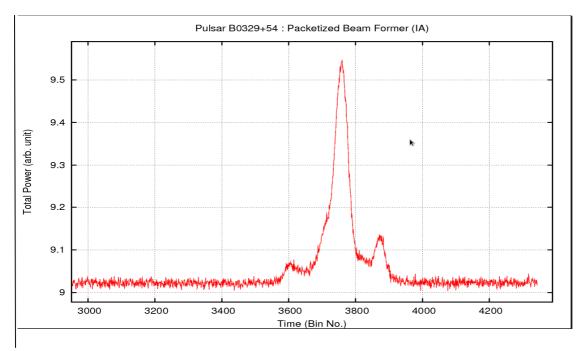

2.TEST : Pulsar test at 400Mhz RF Bandwidth.

- <u>Date of observation</u>: 27<sup>th</sup> November 2013.

- <u>Pulsar</u>: B0329+54

- <u>Antennas used</u>: 4 central square antennas used.

- <u>Sampling clock</u>:800MHz.

- <u>Integration time</u>: 0.164 millisecond

- <u>Beamformer Bandwidth</u>: 400 MHz

- <u>RF Bandwidth</u>: 400 MHz

- <u>Number of channels</u>:512

Figure 8.16 PMON Profile of Pulsar B0329+54 at 400MHz R.F. B.W.

This is the first detection through this design at full 400 MHz RF in the L-Band. Local Oscillator at 1450 MHz.

# 9. Add-on to the Beamformer Subsystem

This section briefly explains the add-ons that have been added to the beamformer subsystem separately.

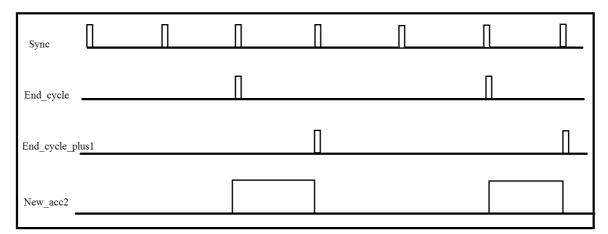

#### 9.1 Add-On:On-board integrator:

Purpose: Used for multiple sync cycle integration.

Working:

- 1) Accumulation is done in Dual Port RAM.

- 2) Three signals are generated: End cycle\_minus 1, end\_cycle plus 1 and end cycle,end\_cycle\_minus1\_ext.

- 3) Registers are used to give a continuous high signal till some desired instant. These registers are enabled and reset accordingly.

- 4) New\_ acc gen:Register reset by end\_cycle plus 1, enable by end cycle 1

- 5) Tx\_valid: Register reset by end\_cycle minus1\_ ext, enable by end cycle minus 1,. Output of this register is added with write enable which is input to this subsystem.

- 6) End of frame: counts 64 tx\_valid and goes high on the 64<sup>th</sup> tx\_valid.

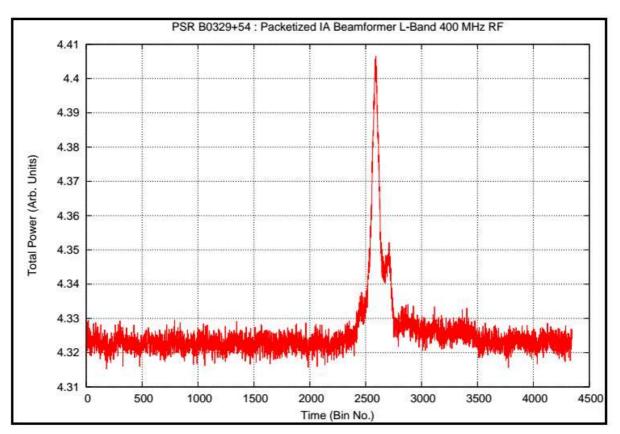

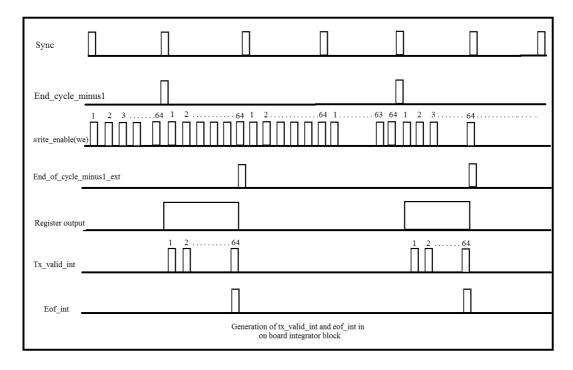

<u>Timing Diagram:</u> Figure 9.1 and 9.2 illustrate the timing diagram for accumulation of 3 sync cycles.

Figure 9.1 Add-on: Generation of new\_acc signal

New\_acc signal should be high for the first sync cycle of every accumulation as it is the select signal to the MUX that selects the second input to the adder.

Figure 9.2 Add-on: Generation of Tx-valid and end of frame.

64 tx valid should come in the last sync cycle of every accumulation and end of frame should go high on every  $64^{\text{th}} \text{ tx}$  valid.

Status: Design is compiled and tested for each X-engine separately. Results are as expected.

<u>Result:</u> Figure 9.3 shows noise test results for 10 integration cycle(green) and 100 integration cycle(red). The results are only for 1 X-engine.

Figure 9.3 Add-on: Multiple Integration Result.

#### 9.2 Add-on:Packet counter:

Purpose: Time synchronized interleaving of packets.

<u>Working</u>: A packet count is added to the data packet after the values for all 64 channels of that X-engine have arrived at the data input of the 10GbE v2 block of that particular X-engine.

Data-packet: It will now be of 520 bytes as 8 byte packet counter is added to the packet.

Figure 9.4 Data packet with packet counter

The UDP packet size will be 520 bytes(data)+42 bytes(header) i.e. 562 bytes.

<u>Timing Diagram</u>: Figure 9.5 shows the timing diagram for 10 GbE signals when a packet count is transmitted along with data.

Figure 9.5 Add-on: 10 GbE signals for packet counter

An extra tx\_valid is generated for the packet count value and the end of frame goes high with this extra tx\_valid. In this case, 65 tx\_valids will be there.

<u>Status</u>: Design checked in simulation. Size of data packet checked in wireshark. It is found to be 520 bytes.

## **10. Future work and recommendations**

- Scale the design to 8 antennas

- Scale the design for greater number of channels

- Attempt time synchronized interleaving using packet counter logic. Develop Post-processing scripts for the same.

- Attempt Sync cycle integration for all 8 X-engines together.

- Analysis of relative improvement in SNR as a function of number of antennas.

## **11. References**

1. Jayaram N Chengalur, Yashwant Gupta, K S Dwarkanath, *—Low Frequency Radio Astronomy*", a note from school on radio astronomy held at NCRA, Pune , 1999.

2.Casper website, <u>https://casper.berkeley.edu/</u>

3. Casper tutorials on ROACH board,

*a.* On Introduction to Simulink, *https://casper.berkeley.edu/wiki/Introduction\_to\_Simulink b.* On The 10GbE Interface, *https://casper.berkeley.edu/wiki/Tutorial\_10GbE c.* On the Wideband Pocket Correlator, *https://github.com/casperastro/ tutorials\_devel/tree/master/workshop\_2010/roach\_tut4\_wideband\_poco*

4. Cambodge bist, - "Pocket Beamformer on FPGA", student project report, NCRA, TIFR

5.Ankur Verma, Subhajit Majumder, —"Designing of Coherent Pocket Beamforemer on FPGA<sup>\*\*</sup>, student project report, NCRA,TIFR

6. Pulsar Period Simulator,

http://astro.unl.edu/classaction/animations/extrasolarplanets/pulsarPeriodSim001.html

### Appendix A APPENDIX A-1

This is a list of the Frequencies that belong to X-engine1 and X-engine 2.

Each X-engine processes 64 channels.

Column 1 shows the Channel in the respective X-engine out of the 64 channels.

Column 3 shows the Channel number for X-engine 1 out of the total 512 channels.

Column 4 shows the Frequencies accepted by X-engine 1 in MHz.

Column 6 shows the Channel number for X-engine 2 out of the total 512 channels.

Column 7 shows the Frequencies accepted by X-engine 2 in MHz.

| Channel | X ENGINE 1 | FREQUENCY | X ENGINE 2 | FREQUENCY |

|---------|------------|-----------|------------|-----------|

|         |            | (MHZ)     |            | (MHZ)     |

| 0       | 0          | 0.00      | 1          | 0.78125   |

| 1       | 8          | 6.25      | 9          | 7.03125   |

| 2       | 16         | 12.50     | 17         | 13.28125  |

| 3       | 24         | 18.75     | 25         | 19.53125  |

| 4       | 32         | 25.00     | 33         | 25.78125  |

| 5       | 40         | 31.25     | 41         | 32.03125  |

| 6       | 48         | 37.50     | 49         | 38.28125  |

| 7       | 56         | 43.75     | 57         | 44.53125  |

| 8       | 64         | 50.00     | 65         | 50.78125  |

| 9       | 72         | 56.25     | 73         | 57.03125  |

| 10      | 80         | 62.50     | 81         | 63.28125  |

| 11      | 88         | 68.75     | 89         | 69.53125  |

| 12      | 96         | 75.00     | 97         | 75.78125  |

| 13      | 104        | 81.25     | 105        | 82.03125  |

| 14      | 112        | 87.50     | 113        | 88.28125  |

| 15      | 120        | 93.75     | 121        | 94.53125  |

| 16      | 128        | 100.00    | 129        | 100.78125 |

| 17      | 136        | 106.25    | 137        | 107.03125 |

| 18      | 144        | 112.50    | 145        | 113.28125 |

| 19      | 152        | 118.75    | 153        | 119.53125 |

| 20      | 160        | 125.00    | 161        | 125.78125 |

| 21      | 168        | 131.25    | 169        | 132.03125 |

| 22 | 176 | 137.50 | 177 | 138.28125 |

|----|-----|--------|-----|-----------|

| 23 | 184 | 143.75 | 185 | 144.53125 |

| 24 | 192 | 150.00 | 193 | 150.78125 |

| 25 | 200 | 156.25 | 201 | 157.03125 |

| 26 | 208 | 162.50 | 209 | 163.28125 |

| 27 | 216 | 168.75 | 217 | 169.53125 |

| 28 | 224 | 175.00 | 225 | 175.78125 |

| 29 | 232 | 181.25 | 233 | 182.03125 |

| 30 | 240 | 187.50 | 241 | 188.28125 |

| 31 | 248 | 193.75 | 249 | 194.53125 |

| 32 | 256 | 200.00 | 257 | 200.78125 |

| 33 | 264 | 206.25 | 265 | 207.03125 |

| 34 | 272 | 212.50 | 273 | 213.28125 |

| 35 | 280 | 218.75 | 281 | 219.53125 |

| 36 | 288 | 225.00 | 289 | 225.78125 |

| 37 | 296 | 231.25 | 297 | 232.03125 |

| 38 | 304 | 237.50 | 305 | 238.28125 |

| 39 | 312 | 243.75 | 313 | 244.53125 |

| 40 | 320 | 250.00 | 321 | 250.78125 |

| 41 | 328 | 256.25 | 329 | 257.03125 |

| 42 | 336 | 262.50 | 337 | 263.28125 |

| 43 | 344 | 268.75 | 345 | 269.53125 |

| 44 | 352 | 275.00 | 353 | 275.78125 |

| 45 | 360 | 281.25 | 361 | 282.03125 |

| 46 | 368 | 287.50 | 369 | 288.28125 |

| 47 | 376 | 293.75 | 377 | 294.53125 |

| 48 | 384 | 300.00 | 385 | 300.78125 |

| 49 | 392 | 306.25 | 393 | 307.03125 |

| 50 | 400 | 312.50 | 401 | 313.28125 |

| 51 | 408 | 318.75 | 409 | 319.53125 |

| 52 | 416 | 325.00 | 417 | 325.78125 |

| 53 | 424 | 331.25 | 425 | 332.03125 |

| 54 | 432 | 337.50 | 433 | 338.28125 |

| 55 | 440 | 343.75 | 441 | 344.53125 |

| 56 | 448 | 350.00 | 449 | 350.78125 |

| 57 | 456 | 356.25 | 457 | 357.03125 |

| 58 | 464 | 362.50 | 465 | 363.28125 |

| 59 | 472 | 368.75 | 473 | 369.53125 |

| 60 | 480 | 375.00 | 481 | 375.78125 |

| 61 | 488 | 381.25 | 489 | 382.03125 |

| 62 | 496 | 387.50 | 497 | 388.28125 |

|    |     |        |     |           |

| 63 | 504 | 393.75 | 505 | 394.53125 |

|----|-----|--------|-----|-----------|

### **APPENDIX A-2**

This is a list of the Frequencies that belong to X-engine 3 and X-engine 4.

Each X-engine processes 64 channels.

Column 1 shows the Channel in the respective X-engine out of the 64 channels.

Column 3 shows the Channel number for X-engine 3 out of the total 512 channels.

Column 4 shows the Frequencies accepted by X-engine 3 in MHz.

Column 6 shows the Channel number for X-engine 4 out of the total 512 channels.